Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Planar GaAs nanowire tri-gate MOSFETs by vapor-liquid-solid growth

Chen Zhang, Xiuling Li\*

Department of Electrical and Computer Engineering, Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Urbana, IL 61801, USA

### ARTICLE INFO

Article history:

Received 23 October 2013

Received in revised form 2 December 2013

Accepted 9 December 2013

Available online 3 January 2014

The review of this paper was arranged by Prof. E. Calleia

Keywords: Metalorganic chemical vapor deposition (MOCVD) Metal-oxide-semiconductor field effect transistor (MOSFET) Nanowire

#### ABSTRACT

Depletion-mode metal-oxide-semiconductor field effect transistors (MOSFETs) with GaAs planar nanowire (NW) channels are successfully demonstrated. The Si-doped planar GaAs NWs are grown in a selective lateral epitaxy manner via Au-assisted vapor-liquid-solid (VLS) mechanism. A  $SiO_2$  interlayer between the multi-faceted NW and  $Al_2O_3$  high-k dielectric formed by atomic layer deposition (ALD) improves the NW MOSFET performance.

© 2013 Elsevier Ltd. All rights reserved.

# 1. Introduction

III-V semiconductor nanowires (NWs) have received much attention recently due to their high intrinsic electron mobility and the inherent 3-dimensional geometry which facilitates the realization of multi-gate transistors [1]. Comparing with top-down approaches, bottom-up vapor-liquid-solid (VLS) growth method is of particular interest since it produces NWs with smooth facets that are free of etching damage. However, conventional VLS NWs grow out of the substrate plane, which makes them incompatible with the well-established planar processing technology and thus prevents them from entering practical electronic applications readily [2]. To address this issue, our group has recently developed a controlled VLS growth method to assemble planar and self-aligned GaAs NWs by metalorganic chemical vapor deposition (MOCVD) [3]. Unlike the out-of-plane NWs, planar NWs are grown laterally and propagate in parallel along  $\langle 110 \rangle$  and  $\langle 100 \rangle$  directions on (100) and (110) substrates, respectively [4]. The planar geometry and self-aligned nature are very attractive in terms of device integration. The epitaxially smooth multi-faceted cross-section profile makes these planar NWs ideal for multi-gate FETs [3-5]. So far high-performance MESFET and HEMT devices have been demonstrated using such planar NWs as the conduction channels [5,6].

In this letter, we further demonstrate planar NW functionality by the successful realization of depletion-mode MOSFETs based on Si-doped n-type planar GaAs NWs using Al<sub>2</sub>O<sub>3</sub> as the gate oxide. For III–V multi-gate transistors, simultaneous passivation of different crystal facets could be challenging since interface trap density has strong crystal orientation dependence [7]. We here use SiO<sub>2</sub> deposited by plasma-enhanced chemical vapor deposition (PECVD) as an interfacial layer between Al<sub>2</sub>O<sub>3</sub> and the GaAs NW surface to further improve the interface quality and device performance [8].

# 2. Growth and fabrication

GaAs planar NWs were grown on (100) semi-insulating GaAs substrate by atmospheric pressure MOCVD at 460 °C utilizing colloidal Au particles (250 nm in diameter) as growth catalysts. Si $_2$ H $_6$  was used as the n-type doping precursor. The NWs, trapezoidal in cross-section, have a bottom width of  $\sim$ 280 nm. Top surface has been identified to be (100) whereas the two sidewalls are (111)A [3,4]. Standard Ge/Au/Ni/Au metal stack is used for S/D contact whereas Ni/Au is used for gate contact. The gate length is measured to be  $\sim$ 850 nm. The nominal thickness for the MOSFET high-k Al $_2$ O $_3$  layer is 7.2 nm. When an interfacial layer of  $\sim$ 1 nm was inserted between the multi-faceted GaAs NW and the high-k Al $_2$ O $_3$  layer, the Al $_2$ O $_3$  thickness was reduced accordingly to 6.3 nm

For capacitance–voltage (C–V) measurements, MOS capacitors (MOSCAPs) were fabricated on commercial n-type doped  $(1-3\times10^{18}~{\rm cm}^{-3})$  GaAs (100) substrates. (100) surface is known to have strong Fermi level pinning due to high interface trap density whereas (111)A is inherently unpinned [7].

<sup>\*</sup> Corresponding author. Tel.: +1 2172656354. E-mail address: xiuling@illinois.edu (X. Li).

### 3. Results and discussion

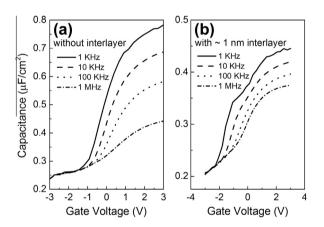

Fig. 1(a) shows the C-V curves of an n-type GaAs MOSCAP with 10 nm Al<sub>2</sub>O<sub>3</sub>. Very large frequency dispersion (0.11 uF cm<sup>-2</sup>/dec at  $V_g = 3 \text{ V}$ ) is observed, indicating poor interface quality [7]. We attempted to deposit an amorphous silicon interlayer between ALD Al<sub>2</sub>O<sub>3</sub> and GaAs by PECVD to improve the interface quality, following [8]. Indeed, much less frequency dispersion (0.024  $\mu$ F cm<sup>-2</sup>/dec at  $V_g = 3 \text{ V}$ ) is observed as shown in Fig. 1(b). However, the asdeposited material was actually SiO<sub>2</sub> because of the residual oxygen in our PECVD chamber. This is confirmed by the fact that the material cannot be etched by XeF2 and the refractive index measured from calibration samples by ellipsometry is 1.44. Never the less, substantial improvement of C-V characteristics can be achieved by using this SiO<sub>2</sub> interlayer as shown in Fig. 1(b). It is likely that the same mechanism as discussed in Ref. [8] applies here since the GaAs-Si interface chemistry should still be the same under the dominantly Si-rich PECVD environment.

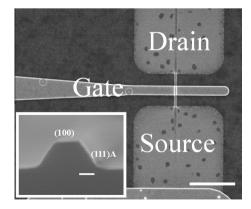

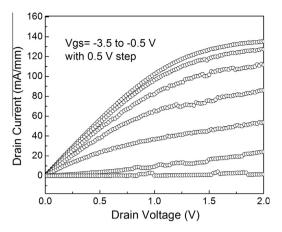

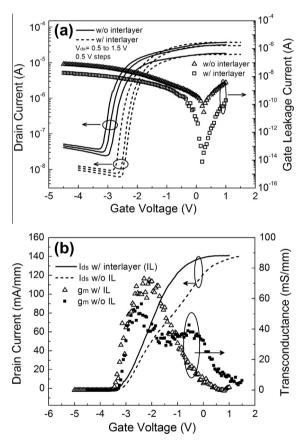

A SEM image of a fabricated GaAs NW MOSFET is shown in Fig. 2. The inset shows the trapezoidal cross-section profile of the NW channel with a (100) top facet and two (111)A side facets, a tri-gate structure. The output characteristics of the device with the interlayer are shown in Fig. 3. Fig. 4(a) shows the comparison of sub-threshold characteristics between the devices with and without  $SiO_2$  interlayer.  $V_{ds}$  varies from 0.5 V to 1.5 V with 0.5 V step for both devices. The sub-threshold slope of the device

Fig. 1. C–V measurement results of  $Al_2O_3/GaAs$  n-type MOSCAPs without (a) and with the  $SiO_2$  interlayer (b).

**Fig. 2.** Top-view SEM image of a fabricated planar NW MOSFET device. The scale bar represents 4  $\mu$ m. The inset SEM image shows the cross section of an as-grown planar NW with a (100) top facet and two (111) A sidewalls [4]. The scale bar in the inset represents 80 nm.

Fig. 3. Output curves of the Planar NW MOSFET device with the SiO<sub>2</sub> interlayer.

**Fig. 4.** (a) Comparison of sub-threshold and gate leakage characteristics between devices with and without the interlayer.  $V_{\rm ds}$  varies from 0.5 V to 1.5 V with 0.5 V step for transfer curves of both devices. The gate leakage current is measured at  $V_{\rm ds} = 0.5$  V. Note that the transfer curves of the device with interlayer are shifted toward right by 0.5 V in order to ensure clarity. (b) Comparison of on-state transfer characteristics between devices with and without interlayer at  $V_{\rm ds} = 2$  V.

without the interlayer is calculated to be 190 mV/dec whereas a better value of 160 mV/dec is obtained for the one with the interlayer. The drain-induced barrier lowering (DIBL) is measured to be  $\sim$ 150 mV/V for both devices. Also shown in Fig. 4(a) is the gate leakage current measured for both devices at  $V_{\rm ds}$  = 0.5 V. It can be seen that the gate leakage is reduced with the help of high-bandgap SiO<sub>2</sub> interlayer. We re-plot the transfer curves in linear scale and calculated the transconductances ( $g_{\rm m}$ ) in Fig. 4(b), normalized with respect to the bottom width of the NW. The peak

extrinsic  $g_m$  is about 73 mS/mm for the device with the interlayer. The intrinsic  $g_m$  is estimated to be about 92 mS/mm by taking into account the source-side series resistance (2.8 k $\Omega$  µm by estimation). These numbers are comparable to the transconductance achieved on thin-film depletion-mode GaAs MOSFETs [9]. For the device without the interlayer,  $g_m$  is lower in general and quickly rolls off after the gate voltage reaches  $\sim$ 1 V beyond threshold. The comparison in Fig. 4 indicates that the NW surface Fermi level can be more effectively moved in the device with the interlayer. In addition, we observe a double-hump feature in the  $g_m$  curve of the device without interlayer, which is presumably related to the presence of two kinds of facets in our planar NW. This feature is seen to be removed (Fig. 4(b)) by applying the interlayer which can improve passivation quality of top (100) facet (Fig. 1), the worse one of the two.

### 4. Conclusion

In conclusion, we have demonstrated planar GaAs NW MOSFETs, which is yet another type of FET successfully achieved after MESFETs and HEMTs using the MOCVD grown, epitaxially smooth and multi-faceted, planar NW platform. A SiO<sub>2</sub> interfacial layer, inserted between GaAs NW and high-k Al<sub>2</sub>O<sub>3</sub> dielectric, improves the interface quality and device performance. The growth of ultrathin planar NW with Indium-containing high electron mobility III–V materials, which are of more interest for digital and RF applications, is currently under study.

## Acknowledgments

This work was supported by NSF ECCS #1001928 (device) and DMR #1006581 (growth).

### References

- [1] Tomioka J, Yoshimura M, Fukui T. A III–V nanowire channel on silicon for high performance vertical transistors. Nature 2012;488(7410):189–92.

- [2] Fortuna SA, Li X. Metal-catalyzed semiconductor nanowires: a review on the control of growth directions. Semicond Sci Technol 2010;25(2):024005.

- [3] Fortuna SA, Wen J, Chun IS, Li X. Planar GaAs nanowires on GaAs (100) substrates: self-aligned, nearly twin-defect free, and transfer-printable. Nano Lett 2008;8(12):4421–7.

- [4] Dowdy RS, Walko DA, Li X. Relationship between planar GaAs nanowire growth direction and substrate orientation. Nanotechnology 2013;24(3):035304.

- [5] Fortuna SA, Li X. GaAs MESFET with a high-mobility self-assembled planar nanowire channel. IEEE Electron Dev Lett 2009;30(6):593–5.

- [6] Miao X, Zhang C, Li X. Monolithic barrier-all-around high electron mobility transistor with planar GaAs nanowire channel. Nano Lett 2013;13(6):2548–52.

- [7] Xu M, Xu K, Contreras R, Milojevic R, Shen T, Koybasi O, et al. New insight into Fermi-level unpinning on GaAs: impact of different surface orientations. Baltimore, MD: IEDM Tech. Dig; 2009. p. 1–4.

- [8] Hinkle CL, Milojevic M, Brennan B, Sonnet AM, Aguirre-Tostado FS, Hughes GJ, et al. Detection of Ga suboxides and their impact on III-V passivation and Fermi-level pinning. Appl Phys Lett 2009;94(16):162101.

- [9] Ye PD, Wilk GD, Kwo J, Yang B, Gossmann H-JL, Frei M, et al. GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition. IEEE Electron Dev Lett 2003;24(4):209–11.